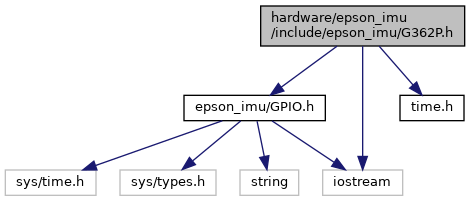

#include <epson_imu/GPIO.h>

#include <time.h>

#include <iostream>

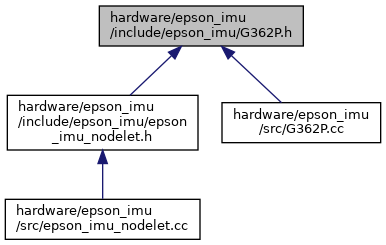

Go to the source code of this file.

|

| enum | epson_imu::Mode { epson_imu::SAMPLING = 0x00,

epson_imu::CONFIGURATION = 0x01

} |

| |

| enum | epson_imu::Window { epson_imu::WIN0 = 0x00,

epson_imu::WIN1 = 0x01

} |

| |

| enum | epson_imu::OutputBits { epson_imu::B16 = 0,

epson_imu::B32 = 1

} |

| |

| enum | epson_imu::Filter {

epson_imu::MOV_AVG_TAP_2 = 0x01,

epson_imu::MOV_AVG_TAP_4 = 0x02,

epson_imu::MOV_AVG_TAP_8 = 0x03,

epson_imu::MOV_AVG_TAP_16 = 0x04,

epson_imu::MOV_AVG_TAP_32 = 0x05,

epson_imu::MOV_AVG_TAP_64 = 0x06,

epson_imu::MOV_AVG_TAP_128 = 0x07,

epson_imu::FIR_TAP_32_FC_50 = 0x08,

epson_imu::FIR_TAP_32_FC_100 = 0x09,

epson_imu::FIR_TAP_32_FC_200 = 0x0A,

epson_imu::FIR_TAP_32_FC_400 = 0x0B,

epson_imu::FIR_TAP_64_FC_50 = 0x0C,

epson_imu::FIR_TAP_64_FC_100 = 0x0D,

epson_imu::FIR_TAP_64_FC_200 = 0x0E,

epson_imu::FIR_TAP_64_FC_400 = 0x0F,

epson_imu::FIR_TAP_128_FC_50 = 0x10,

epson_imu::FIR_TAP_128_FC_100 = 0x11,

epson_imu::FIR_TAP_128_FC_200 = 0x12,

epson_imu::FIR_TAP_128_FC_400 = 0x13

} |

| |

| enum | epson_imu::SamplingRate {

epson_imu::SPS2000 = 0x01,

epson_imu::SPS1000 = 0x02,

epson_imu::SPS500 = 0x03,

epson_imu::SPS250 = 0x04,

epson_imu::SPS125 = 0x05,

epson_imu::SPS62_5 = 0x06,

epson_imu::SPS31_25 = 0x07

} |

| |

◆ ARRAY_SIZE

| #define ARRAY_SIZE |

( |

|

a | ) |

(sizeof(a) / sizeof((a)[0])) |

◆ CHECK_REG_VALUE

| #define CHECK_REG_VALUE 1 |

◆ EPSON_POWER_ON_DELAY

| #define EPSON_POWER_ON_DELAY 800000 |

◆ REG_BURST_CTRL1_H

| #define REG_BURST_CTRL1_H 0x0C |

◆ REG_BURST_CTRL1_L

| #define REG_BURST_CTRL1_L 0x0D |

◆ REG_BURST_CTRL2_H

| #define REG_BURST_CTRL2_H 0x0E |

◆ REG_BURST_CTRL2_L

| #define REG_BURST_CTRL2_L 0x0F |

◆ REG_BURST_H

◆ REG_BURST_L

◆ REG_COUNT

◆ REG_DIAG_STAT_H

| #define REG_DIAG_STAT_H 0x04 |

◆ REG_DIAG_STAT_L

| #define REG_DIAG_STAT_L 0x05 |

◆ REG_FILTER_CTRL_H

| #define REG_FILTER_CTRL_H 0x06 |

◆ REG_FILTER_CTRL_L

| #define REG_FILTER_CTRL_L 0x07 |

◆ REG_FLAG_H

◆ REG_FLAG_L

◆ REG_GLOB_CMD_H

| #define REG_GLOB_CMD_H 0x0A |

◆ REG_GLOB_CMD_L

| #define REG_GLOB_CMD_L 0x0B |

◆ REG_GPIO_H

◆ REG_GPIO_L

◆ REG_MODE_CTRL_H

| #define REG_MODE_CTRL_H 0x02 |

◆ REG_MODE_CTRL_L

| #define REG_MODE_CTRL_L 0x03 |

◆ REG_MSC_CTRL_H

| #define REG_MSC_CTRL_H 0x02 |

◆ REG_MSC_CTRL_L

| #define REG_MSC_CTRL_L 0x03 |

◆ REG_SIG_CTRL_H

| #define REG_SIG_CTRL_H 0x00 |

◆ REG_SIG_CTRL_L

| #define REG_SIG_CTRL_L 0x01 |

◆ REG_SMPL_CTRL_H

| #define REG_SMPL_CTRL_H 0x04 |

◆ REG_SMPL_CTRL_L

| #define REG_SMPL_CTRL_L 0x05 |

◆ REG_TEMP_HIGH

| #define REG_TEMP_HIGH 0x0E |

◆ REG_TEMP_LOW

| #define REG_TEMP_LOW 0x10 |

◆ REG_UART_CTRL_H

| #define REG_UART_CTRL_H 0x08 |

◆ REG_UART_CTRL_L

| #define REG_UART_CTRL_L 0x09 |

◆ REG_WIN_CTRL_H

| #define REG_WIN_CTRL_H 0x7E |

◆ REG_WIN_CTRL_L

| #define REG_WIN_CTRL_L 0x7F |

◆ REG_XACCL_HIGH

| #define REG_XACCL_HIGH 0x1E |

◆ REG_XACCL_LOW

| #define REG_XACCL_LOW 0x20 |

◆ REG_XGYRO_HIGH

| #define REG_XGYRO_HIGH 0x12 |

◆ REG_XGYRO_LOW

| #define REG_XGYRO_LOW 0x14 |

◆ REG_YACCL_HIGH

| #define REG_YACCL_HIGH 0x22 |

◆ REG_YACCL_LOW

| #define REG_YACCL_LOW 0x24 |

◆ REG_YGYRO_HIGH

| #define REG_YGYRO_HIGH 0x16 |

◆ REG_YGYRO_LOW

| #define REG_YGYRO_LOW 0x18 |

◆ REG_ZACCL_HIGH

| #define REG_ZACCL_HIGH 0x26 |

◆ REG_ZACCL_LOW

| #define REG_ZACCL_LOW 0x28 |

◆ REG_ZGYRO_HIGH

| #define REG_ZGYRO_HIGH 0x1A |

◆ REG_ZGYRO_LOW

| #define REG_ZGYRO_LOW 0x1C |

◆ SF_ACCL

◆ SF_GYRO

◆ SF_TEMP

| #define SF_TEMP (0.0042725) |

◆ STALL_BURST_MODE_BEFORE_DATA

| #define STALL_BURST_MODE_BEFORE_DATA 45 |

◆ STALL_BURST_MODE_BETWEEN_DATA

| #define STALL_BURST_MODE_BETWEEN_DATA 5 |

◆ STALL_NORMAL_MODE

| #define STALL_NORMAL_MODE 20 |